הטיפ של CUI: כיצד להוביל 100A אל נקודת העומס

פורסם ב-פברואר 22, 2015

המעבדים היום דורשים מתחי האספקה של 1V ופחות, אולם, הם בעלי הספק של 100W ויותר. כלומר הם מציבים אתגר מיוחד במינו: כיצד להביא זרמים בערכים של כ-100A אל נקודות העומס (Point of Load)

המעבדים היום דורשים מתחי האספקה של 1V ופחות, אולם, הם בעלי הספק של 100W ויותר. כלומר הם מציבים אתגר מיוחד במינו: כיצד להביא זרמים בערכים של כ-100A אל נקודות העומס (Point of Load)

מאת: Dr. Fariborz Musavi, CUI Inc

חוק Moore הביא לנו כמויות אדירות של כוח מחשוב באמצעות מיקרו-מעבדים מיקרו ורכיבי FPGA מתקדמים. אולם כדי להפעיל את הרכיבים החדשים מתכנני המעבדים ורכיבי FPGA היו צריכים להוריד את מתחי האספקה ל-1 וולט או פחות, מכיוון שמתחים גבוהים יותר היו עלולים לגרום נזק בלתי הפיך למעגלים הלוגיים הפועלים במהירות גבוהה.

כתוצאה מכך, מתחים בתחום 1.8V-3V משמשים רק בהתקנים ייעודיים של כניסות ויציאות המתחברים בממשק לזיכרון ולהתקנים היקפיים. אך מעטפת ההספק המרבי של מעבדים ורכיבי FPGA היא עדיין בסדר גודל של כמה עשרות ואטים, ומתקרבת ל-100 ואט עבור המוצרים בעלי ביצועים גבוהים. התוצאה: דרישה המתחילה לחרוג מרמה של 100 אמפר (100A) בנקודת העומס (Point of Load).

הגישה המסורתית

שינויים אלו יכולים היו להיתמך על-ידי ארכיטקטורות מסורתיות, אם היינו מקדישים יותר מקום לממירי POL ולקבלי ביטול הצימוד. ואולם, ברוה המערכות המתקדמות מצטמצם המקום הזמין במעגל המודפס. בנוסף, תכנון מעגל המרת מתחים הפועל זזרם גבוה דורש מומחיות רבה, שאינה נמצאת בידי רוב מפתחי המעגלים התומכים במעבדים החדשים.

תכנון אספקת מתח לנקודת העומס בזרם גבוה ובמתח נמוך הוא אתגר מורכב מכיוון שהפסדי ההולכה יחסיים לריבוע זרם המוצא (I2out), עם התנגדות לזרם ישר (DC) בתוך המשרנים, וכן בטרנזיסטורי ההספק ובצורת החיווט, אשר תורמים את חלקם באופן משמעותי. בעיה נוספת היא הפסדי המיתוג. במהלך מעברי המיתוג, למתג הבקרה יש הפסדי מיתוג יחסיים ל-Iout×Ein ולמשך הזמן של מעבר המיתוג.

מהירות המיתוג נשלטת בחלקה על-ידי מהירות ה-gate בטרנזיסטור ההספק, שהיא מוגבלת בגלל ההשראה הפרזיטית בחיבור source. בגלל השראה זו, טרנזיסטור MOSFET יכול להמשיך להוליך זרם, אפילו שמתח חיבור gate הגיע ל-0 וולט: נוכחותו של כוח אלקטרו-מניע חוזר שלילי (EMF) הנגרם מההשראה הפרזיטית, מושכת את החיבור ה-source לרמה שלילית ביחס לחיבור ה-gate.

יש צורך בגישה שונה

שיפורים שונים שנעשו ב-Rdson של ההתקן, באופייני המיתוג ובמנגנון הדחיפה שיפרו את מעטפת הנצילות לרמה בשלה מאוד, כזו שקשה מאוד להשיג בה שיפורים נרחבים באמצעות טכניקות תכנון מסורתיות. כדי לטפל במתחים נמוכים ובזרמים גבוהים, יש צורך בהתבוננות רעננה בממיר מוריד מתח (Buck Converter).

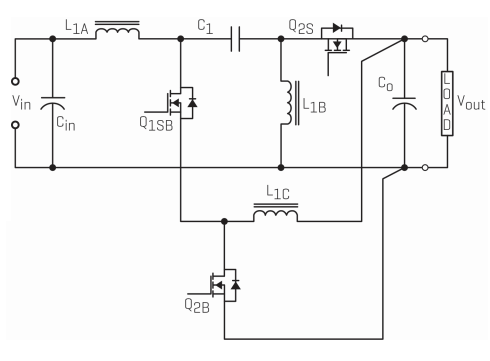

טופולוגיית ממיר מוריד מוזן ממיר (SEPIC-fed buck) למשל, יכולה לשפר את נצילות המרת המתח והתגובה לתופעות מעבר, תוך כדי שמירה על הפשטות והעלות הנמוכה של ממיר מתח מוריד סינכרוני. כך אנו נותנים מענה הן להפסדי המוליכות (סכום של הפסדי מוליכות והפסדי התנגדות לזרם ישר של המשרן) וגם להפסדי המיתוג. על מנת להתגבר על הפסדי I2outR בממיר המתח המוריד, משתמשים בנתיבי העברת אנרגיה מרובים לפיצול זרם העומס. כך מתקבלת התוצאה של הפחתת הפסדי מוליכות בערך הריבועי של הקטנת הזרם.

נתיבי זרם מפוצלים

הקטנת ההתנגדות לזרם ישר באמצעות המשרנים של מעגלים עבור מחזורי העבודה הקטנים יותר, באמצעות טופולוגיה מפוצלת עם מתחי מוצא נמוכים, תורמת להקטנת ההפסדים. נתיבי הזרם המרובים, שהם מהותיים לטופולוגיית ממיר מוריד מוזן מקטינים את מאמצי המתח על הרכיבים בכ-50%. כתוצאה מכך אפשר להשתמש בטופולוגיה זו בטרנזיסטורי MOSFET ובקבלים למתח נמוך יותר מאשר בתכנון רגיל של ממיר מוריד.

מאחר שהתקני מתח נמוך נוטים להציג מוליכות גבוהה יותר, אפשר בטופולוגיה זו להשתמש בטרנזיסטורי MOSFET עם Rdson אופייני נמוך יותר בהשוואה לתכנונים שווי-ערך של ממיר מוריד בלבד, ולקבל הקטנה נוספת של הפסדי המוליכות. בנוסף, השילוב של ממיר SEPIC וממיר מוריד מאפשר את הזרמת זרם הכניסה ואת אספקת זרם העומס ברציפות. כאשר החלק של הממיר המוריד יעבור למצב כבוי, ממיר SEPIC יהיה פעיל, ולהפך.

טופולוגיית ממיר מוריד מוזן SEPIC גם מתגברת על כמה בעיות הקשורות בהפסדי מיתוג של ממירים מורידים רגילים, כגון ההשהיה בכיבוי חיבור gate. יתר על-כן, היא מאפשרת כיבוי מהיר במיוחד באמצעות מנגנון סילוק מטען בחיבור gate המובנה בטופולוגיה, שגם פועל נגד הכוח האלקטרו-מניע החוזר הנגרם מההשראה הפרזיטית ב-source.

בגלל המאמצים הנמוכים יותר של המתח והזרם שקיימים במתגי ההספק, גם הפסדי המצב הפתוח שלהם מופחתים באופן משמעותי.

מיתוג מהיר ורכיבים פסיביים קטנים

רמות הזרם המופחתות בארכיטקטורה זו יגרמו לתגובה מהירה יותר בדרגת ההספק. שיפורים אלו הופכים להיות מרתקים אף יותר בתדירויות מיתוג גבוהות, אשר בהן צפיפות ההספק הכוללת משתפרת. בדיקות שביצענו עם טופולוגיה זו (שם המותג שלה בחברת CUI הוא: Solus® Power Topology) מראות שגם אם משתמשים באותם התקני מיתוג כמו אלו ששימשו בתכנון ממיר מוריד, הטופולוגיה הזו יכולה להפחית את הפסדי המיתוג ביותר מ-90%. כתוצאה מכך, ממיר המבוסס על טופולוגיה זו יפעל בתדרי מיתוג גבוהים ויוכל להשתמש ברכיבים פסיביים קטנים יותר.

בארכיטקטורה זו יש יתרונות נוספים עבור תכנונים המספקים יציאות מתח נמוך ממתח ביניים גבוה יותר. כאשר יחס ההורדה, M, של המתח בין היציאה לכניסה יהיה בתחום שבין 0.100 ל- 0.250, ההפסדים בטופולוגיה זו יהיו טובים ב-91% וב- 88%, בהתאמה, מאשר בטופולוגיית מייצב מתח מוריד רגיל. כאשר היחס גדל ל-0.66 – יתרון הנצילות יהיה 70%. לכן הטופולוגיה הזו מתאימה במיוחד ליישומי אספקה בנקודת העומס, שלהם מתאים יחס המרה רחב.

החטאת המטרה

הלחץ לספק נצילות אנרגיה ממערכות זרם גבוה ומתח נמוך דורש שהמעבדים ולוגיקת התמיכה יידרשו לעבור לעתים קרובות למצבי שימוש בהספק נמוך, עם יכולת חזרה מהירה לעבודה בתפוקה מלאה מבלי להיפגע מסטיות מתח. לדוגמה, סטיית מתח של 2% בלבד יכולה לגרום לכיבוי זמני. המשמעות יכולה להעיות למשל הפסקת חיפוש באינטרנט או ניתוק תקשורת VoIP.

אולם הזרם המוקטן במשרנים משפר גם את התגובה לתופעות מעבר. בכך שהזרם העובר דרך משרני השילוב ירד למחצית, כמעט, ביחס לזרם העומס בכל דרגה, זרם המוצא יכול היה לעלות במהירות כפולה, כמעט, ממה שהיה יכול עם ממיר מוריד רגיל.

כאשר משתמשים בארכיטקטורת ממיר מוריד מוזן ממיר SEPIC, השינויים במתח מאפשרים לזרם לרדת בקצב מהיר פי ארבעה כמעט יותר מאשר אם משתמשים בממיר מוריד בזמן הכיבוי. לכן, דרגת ההספק מהירה יותר באופן מובנה בשני המצבים. התגובה המשופרת לתופעות מעבר מקטינה את המספר והגודל של קבלי ביטול הצימוד הנדרשים על המעגל המודפס, עובדה שמתורגמת לחיסכון נוסף בשטח המעגל.

הוספת בקרה ספרתית

טופולוגיה זו מטפלת בבעיות רבות הקשורות בסטיות מתח שמקורן במדרגת מעבר בעומס, והיא מאפשרת פעולה יציבה, במיוחד בשינויים מהירים. עם זאת, חיבור טופולוגיה זו עם בקר הספק ספרתי מתקדם, מאפשר לקבל תת-מערכת הספק מבוקרת באופן ספרתי. השימוש במעגל בקר ספרתי מאפשר לממש פונקציות פיצוי ובקרה מתקדמות בהרבה מאשר אפשר לקבל בתכנונים מסורתיים מבוססי מעגלים אנלוגיים. יתרון נוסף של מייצבי מיתוג ספרתיים הוא שאפשר לבצע בקלות ובאופן אוטומטי את התאמת הביצועים של המעגל.

בעבר, פונקצית הפיצוי במייצב מתח ספרתי הייתה ממומשת באופן ידני, כלולאות בקרה יחסיות אינטגרליות ודיפרנציאליות (PID). מלכתחילה, פעולה זו הייתה מתבצעת בעזרת כלי ששימש את המהנדס, שעמו הזין את כל רכיבי העברת מתח החיצוניים, ולאחר מכן אותו כלי היה מספק את כל נתוני PID עבור הממשק הגרפי. התנהגות כל אחד מהנתונים הייתה מבוקרת באמצעות מקדמים של כל אחד מהם, והשילוב שלהם קבע את התגובה של מייצב המתח. שיטה זו הייתה טובה יותר מאשר תרשים אנלוגי, אבל עדיין הייתה סטטית ומוכוונת יותר לתנאים הקיימים במצבים הגרועים ביותר.

בקרה דינמית של חוג PID ספרתי, שבה אפשר היה לתכנת באופן דינמי את המקדמים, איפשרה לקבוע בזמן אמת ובתנאים מדויקים את הקונפיגורציה של מייצב המתח, ולבצע בקרה שלו. בקרה כזו סיפקה מעגל שפועל באופן יציב יותר ואפשרה לנטר את התנהגות המערכת ולבצע כיוון מחדש של מעגל מייצב המתח לאורך חיי השימוש במוצר. יתרון חשוב של המימוש הספרתי נעוץ בעובדה שהוא מאפשר יצירת ארכיטקטורות בקרה גמישות, כמו למשל לאפשר את פעולתם של חוגי בקרה מרובים במקביל.

לטופולוגיית הממיר המוריד המוזן SEPIC נדרש בקר ספרתי המתאים ליכולות התגובה ולהרחבות הביצועים הכוללות. ואולם, פונקציונליות זו משולבת בתוך חלק מבקרי PWM (אפנון רוחב אות) המתקדמים ביותר – למשל טכנולוגית ChargeMode של Intersil המשמשת בבקר הספרתי שלה ZL8800 בעל המופע הכפול, שנמצא בשימוש בממירים המתקדמים ביותר של CUI. בקר ZL8800 בעל פיצוי אפס, תומך בשילוב של בקרי חוג אחידים ובקצבים מרובים, טכניקה שמאפשרת אספקה של מתח יציב בד בבד עם תגובה מהירה על שינויים פתאומיים בתנאים.

ליחידת הפיצוי שבתוך הבקר יש שני נתיבים מקבילים לעיבוד מתח שגיאה שנדגם בקצב גבוה. האחד נקרא "נתיב מהיר", והוא דוגם מתח שגיאה בתדירות רבה יותר מאשר "הנתיב האיטי". בשימוש במבנה החדשני של יחידת הפיצוי, הפקודה למחזור העבודה מוזנת חזרה, כדי לקבוע את ההשפעה של הנתיב המהיר וכדי לאפס את השפעת הנתיב המהיר במחזורים הבאים. אסטרטגיה זו הופכת למקומית את ההשפעה של שינוי המתח למספר מחזורים מועט, כדי למנוע את חוסר היציבות שמאפיין אסטרטגיות בקרת PID מתוחכמות פחות, שהותאמו במיוחד באופטימיזציה לתגובה מהירה.

הצירים X, Y ו- Z

גם עם שינויים שבוצעו בארכיטקטורה הפנימית ושולבו כדי ליצור ממיר קומפקטי ביותר בעל נצילות גבוהה לנקודת העומס, עדיין יש מקום ללחצים על ספקי הכוח. מהנדסים נתונים באופן אוניברסאלי כמעט בלחץ קשה כדי לשמור את שטח המעגל המודפס בגודל מזערי.

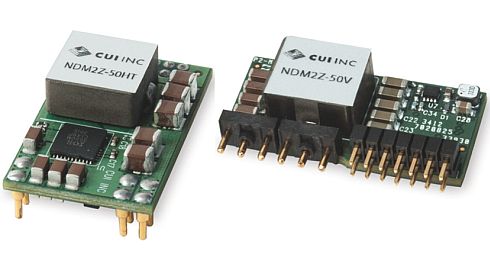

המטרה של מודול אספקת מתח היא ליצור גודל פיסי קומפקטי, אשר מנצל בצורה מרבית את היתרון של ממדי X, Y ו- Z הזמינים. המעבר לזרמים של 100 אמפר ויותר, יגרום למהנדסים להפוך ליצירתיים יותר ולחשוב לא רק במונחים של שטח מעגל מודפס בלבד, אלא גם במונחים של נפח מעגל מודפס. והחברות עושות ככל שביכולתן כדי לעמוד בדרישות האלו, למשל על-ידי הצעה של ספקים לנקודת העומס בשתי גרסאות של ממדים פיסיים, בגרסה שטוחה (פרופיל נמוך) ובגרסה אנכית ("גורד שחקים"). לעתים, ציר Z לא מוגבל, לפעמים הוא מוגבל ביותר. יש לתת היום מענה לכל האפשרויות.

סיכום

חוק Moore העניק לנו כמויות עצומות של כוח מחשוב. ואולם עם הרגישות הגבוהה של המעבדים הקיימים היום, שמורידים את המתחים כלפי מטה, אל מתחת ל-1 וולט עבור ליבת ההתקן, ועם ההספק הנדרש עבור מוצרים בעלי הביצועים הגבוהים ביותר, שיכול להגיע ל-100 ואט או יותר, הדרישה לזרם מתחילה לחרוג מ-100 אמפר.

למקום יש חשיבות עליונה ולכן השיטות המסורתיות שמשתמשות ברכיבים גדולים כדי לטפל במאמצים הגבוהים הקשורים בכך, אינן מעשיות. במקום זאת, כדי לעבור ל- 100 אמפר ויותר, יהיה צורך בהמצאתיות ובחשיבה מופשטת בהרבה חזיתות.